Overview of the RiskX Single Board Computers and Oberon Operating System

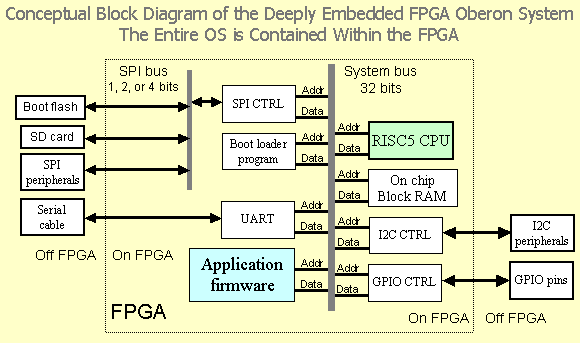

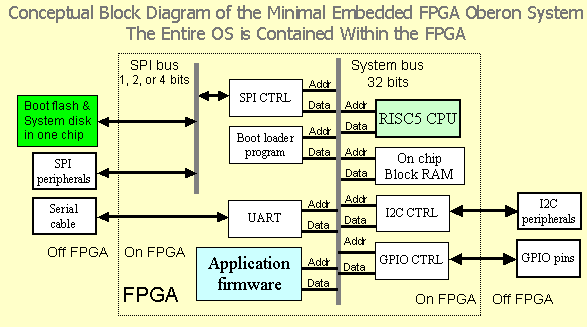

Synopsis. The Risk project aims at creation of instruments running the FPGA Oberon System. The instruments will be built around Field Programmable Gate Arrays (FPGA). They will not provide any conventional CPU such as x86 or ARM. The FPGAs will run a real time Oberon operating system with the help of an embedded soft processor core named RISC5.

Motivation. The Oberon System, being real time and small size, is a great candidate for controlling instrumentation. Linux, which is often used for this purpose, has a much larger memory footprint, complexity, sluggish interrupt handling, lack of determinism, and substantial development effort. A much smaller Oberon System can be a better tool for developing efficient low cost instruments.

Background information. The single user workstation Oberon System was originally developed in mid 1980's. A new edition of this OS was released by Professor Niklaus Wirth and Paul Reed in 2013 for the Spartan-3 FPGA. Since then several implementations were developed for Spartan-6, Spartan-7, and Artix-7. The same FPGA Oberon System is also running under emulated FPGA environments on a PC. Please check the Web resources page for more information.

The original Oberon System was a complete workstation with its own GUI, keyboard, mouse, and a disk file system. It ran on an academic 32-bit machine with 2 MB of dynamic RAM and 256 kB of video RAM. It used a 32-bit processor NS32032 clocked at 10 MHz. The system could self-compile itself. The same is now true under the 2013 FPGA Oberon System. Cross development is also supported. Several PC-based emulators are available where one can cross develop software and download it to the board for execution.

Hardware, firmware, software. The FPGA Oberon System needs a hardware board with a sufficiently large FPGA for hosting its firmware, whose primary component is the RISC5 soft processor core running the Oberon System software. There are Oberon projects out there which rely solely on the third party boards (e.g., Astrobe). We have chosen to develop our own boards in order to future proof the project against the third party boards being pulled out of market.

Customizable general purpose computer. The FPGA Oberon System is a general purpose computer which can be customized to a particular application. The customization can be either in software, firmware, or both. Firmware is adding a new dimension to customization. The computer can be augmented with coprocessors, state machines, streaming interfaces, or custom peripherals. Firmware customization is outside the realm of conventional single board computers such as Arduino or Raspberry Pi.

Applications. We plan to use the Oberon System to develop reliable embedded software for instrumentation. We plan to adopt both the Workstation and the Embedded variants for this purpose (explained below).

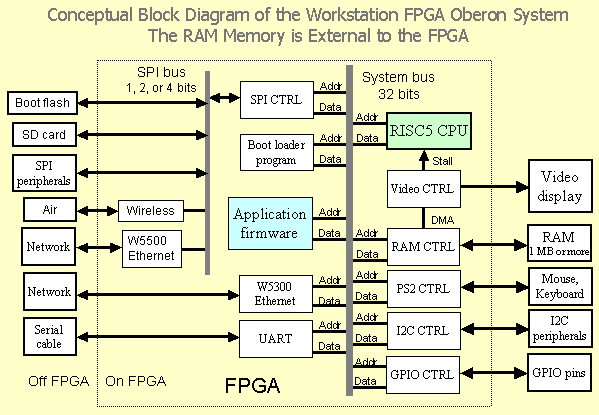

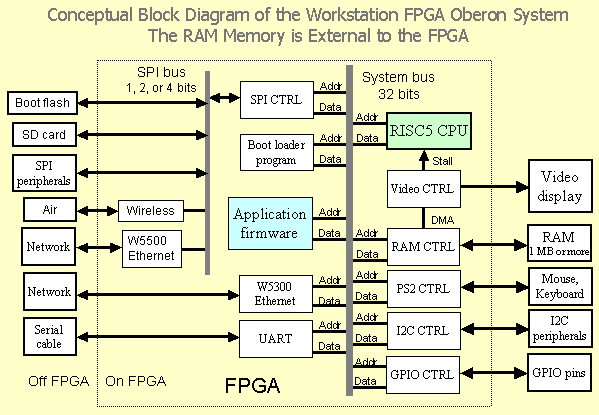

There are two major variants of the FPGA Oberon System. The Workstation Oberon System can be used for in situ software development, using the workstation itself. The diagram shows the major components of the workstation. Not all of them have to be present. The minimal configuration comprises the solid state disk (i.e., the SD card), mouse, keyboard, and video monitor display. The workstation software comprises the compiler, loader, run time system, device drivers, and the graphical user interface. The workstion can run with a single megabyte of RAM.