Firmware for RiskFive.

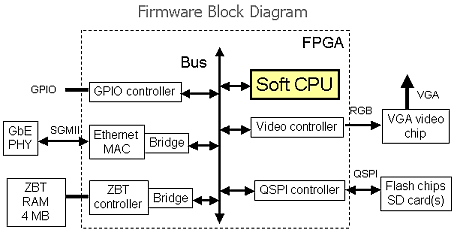

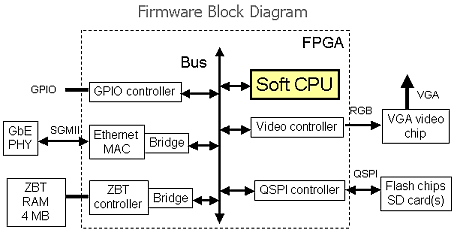

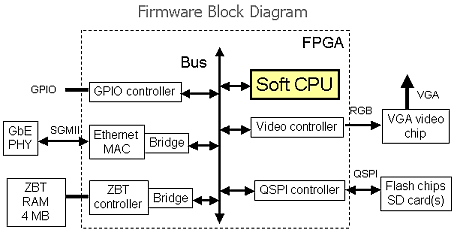

The functionality of the FPGA based system is defined by its firmware (FW), which is usually composed of reusable FW cores, also known as intellectual property (IP) cores. Inside the FPGA project, the IP cores are often connected with a bus exchanging the data, address, and control signals between the cores. FPGA firmware architecture can be broadly divided into two classes A and B.

A.

Firmware consists of logic elements (logic gates, flip flops, etc.) arranged into a programmable logic network which encodes a desired algorithm. Despite its name (coined by Xilinx) the network can not be programmed in the classic sense. The "programming" is performed during firmware development by selecting various logic elements and their connections. Once such a firmware is compiled and loaded into the FPGA, its functionality is fixed.

B.

In addition to the programmable logic, firmware can also incorporate one or more processor cores, which can be either soft or hard. (Hard silicon cores are out of our scope.) The processor cores enable programming in the classic sense, using programming languages such as C, Pascal, or Oberon. Xilinx coined the term processing system to describe the processor cores inside the FPGA. The processing systems can be further subdivided into two classes B1 and B2.

B1.

The processing system can be fully embedded in the FPGA without using external memory. Xilinx coined a term Controller System (CS) to such a fully embedded CPU. The CS software has to be cross compiled using a workstation PC.

B2.

The processing system can have access to external memory and other peripherals. An entire computer can be built around the soft CPU, with a mouse, keyboard, display, and external storage. The FPGA Oberon System is an example of such a complete computer, which can run a compiler and thus it can compile software for itself.

Sources of Firmware IP Cores.

- Excellent textbooks written by Professor Pong P. Chu can be found by searching for "Xilinx MicroBlaze MCS SoC".

- An open source core repository OpenCores.

- Other open source cores available on the net, such as the FPGA Oberon repository.

- Firmware cores provided by the Xilinx development tools.

- Firmware cores described in Xilinx Application Notes.

- Firmware cores developed by ourselves.

The IP cores are serving (or "driving") major hardware features of the development system: the ZBT memory, the flash memory chips, gigabit Ethernet PHY, and the VGA video controller. Most hardware features reside on the motherboard: two more Ethernet chips, RS-232 driver, and USB-3 interface. For clarity we are not showing these extra IP cores in the diagram.

There are several implementations of the bus interconnecting the IP cores. A simple bus named FPro was developed by Pong P. Chu for his textbook mentioned above. Several Fpro cores are available from the book's website. A short introduction to Fpro from the George Mason University (the ECE 448 course) is available online.

An industrial strength Wishbone is often used in both hobby and industrial projects. Another bus was developed by Professor Niklaus Wirth for his FPGA Oberon. Fortunately, all these buses are quite similar to one another.

Soft CPU cores.

RiskFive hardware can accomodate any soft CPU which fits into the board's FPGA. Examples include the MicroBlaze microcontroller provided by Xilinx and used in the Chu's textbook. Another example is RISC5 developed by Professor Niklaus Wirth and available from the FPGA Oberon website. Yet another example is RISC-V developed at Berkeley and adopted in several industrial projects. A whole variety of soft processors are also available from Open Cores. One should note that despite their similar names RISC5 and RISC-V are very different processors. The former is intentionally very simple in order to aid student's understanding. The latter is a fairly complex design targeting heavy duty industrial projects.

User Constraint Files (UCF).

The User Constraint Files (UCF) for the ABone + Motherboard system are available to download from the Design Resources page.

Please inquire concerning other specs and details that have not been covered above.

Updated Feb/07/2022.

© 2018-2022 by SkuTek.com.