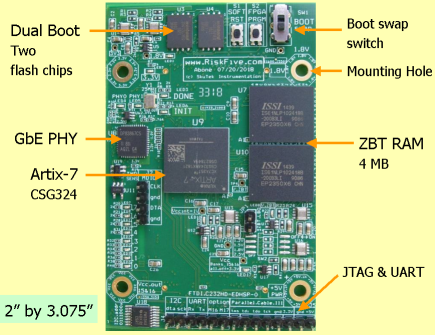

FPGA On Module.

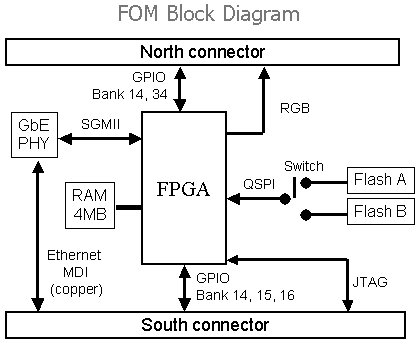

The FPGA On Module (FOM) is shown below. It is a small plugin board with the core hardware: the FPGA, the boot flash, the RAM memory, the gigabit Ethernet transceiver (PHY), and power. The FOM will be hosted by a motherboard providing other functions: the SD card, USB, video, and other connectors needed for a particular application. The FOM will be connected to a motherboard with two high-density Hirose connectors, secured with four mounting screws.

Major Features.

Technical specs.

Please inquire concerning other specs and details that have not been covered above.

Purchasing the RiskFive FPGA System.

The boards will be available for purchase soon. Please inquire by sending an e-mail from the contact page.